Un nuovo consorzio industriale vuole stabilire uno standard di interconnessione die-to-die per i microchip. Si chiama Universal Chiplet Interconnect Express (UCIe) e supporterà un ecosistema di chiplet aperto. Intel ha fornito la specifica UCIe 1.0.

Il nuovo consorzio UCIe è composto da AMD, Arm, Advanced Semiconductor Engineering, ASE, Google Cloud, Intel, Meta (Ex Facebook), Microsoft, Qualcomm, Samsung e TSMC. Grande assente Nvidia.

Di cosa parliamo nel dettaglio.

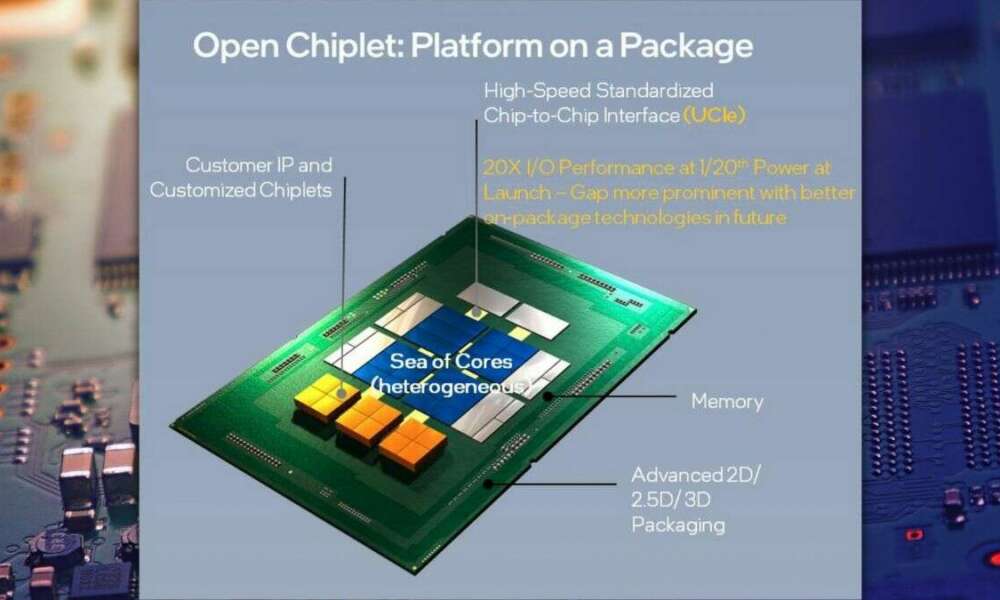

La specifica UCIe 1.0 è un’interconnessione die-to-die standardizzata completa. Comprende un livello fisico, uno stack di protocollo, un modello software e test di conformità. Mappa nativamente i protocolli PCI Express (PCIe) e Compute Express Link (CXL). Le specifiche consentiranno agli utenti finali di combinare stampi e altri componenti di chiplet da più fonti con diverse opzioni di packaging.

Come con altre implementazioni di chiplet, possono esserci core di calcolo fabbricati sul nodo di processo più avanzato, mentre la memoria e il controller IO, ad esempio, possono essere di una generazione precedente, a tutto vantaggio della catena logistica. Ciò non solo ottimizza i costi dei semiconduttori, ma consente di risparmiare la spesa per il porting di quell’IP e la sua convalida.

Un livello fisico ottimizzato è definito sia per l’imballaggio standard (2D) (packaging) che per l’imballaggio avanzato (2,5D), come mostrato nella figura seguente. A destra sono raffigurate diverse opzioni di packaging utilizzate da alcune delle società fondatrici, cioè Intel, TSMC e ASE.

Gli standard attuali CXL e PCIe affrontano una serie di casi d’uso. Debendra Das Sharma di Intel ha partecipato alla scrittura del white paper e osserva: “Con PCIe e CXL, la costruzione di SoC, la gestione dei collegamenti e le soluzioni di sicurezza già implementate possono essere sfruttate in UCIe”…“Anche i modelli di utilizzo affrontati sono esaurienti: il trasferimento dei dati tramite l’accesso diretto alla memoria, il rilevamento del software, la gestione degli errori, ecc., sono affrontati con PCIe/CXL.io; i casi d’uso della memoria vengono gestiti tramite CXL.Mem; e i requisiti di memorizzazione nella cache per applicazioni come gli acceleratori vengono risolti con CXL.cache. UCIe definisce anche un “protocollo di streaming” che può essere utilizzato per mappare qualsiasi altro protocollo”.

Costruire SoC (System on chip) che superano la dimensione massima del reticolo è un obiettivo chiave del nuovo standard. Si mira anche a ridurre i tempi su tutta la filiera consentendo anche il riutilizzo degli stampi, con evidenti vantaggi sui costi.

Una delle cose più interessanti di questo annuncio è il numero delle aziende che si stanno unendo per guidare lo standard. Ciò testimonia il fatto che più il design e il packaging diventano impegnativi e costosi maggiore è la necessità di collaborazione.

UCIe aprirà la strada alla combinazione di dispositivi di aziende concorrenti su un SoC?

Questo nei fatti sta già accadendo con la prossima GPU Ponte Vecchio di Intel, che utilizza i die N5 di TSMC oltre a una serie di altri die fabbricati da Intel. Il nuovo standard quindi crea le condizioni per la produzione di Soc ibridi.

“L’intero scopo di UCIe è creare un ecosistema di chiplet aperto e interoperabile”, ha affermato Das Sharma. Le specifiche UCIe supportano due ampi modelli di utilizzo: integrazione a livello di package e connettività fuori package. Nel primo caso, i componenti collegati a livello di scheda, come memoria, acceleratori o dispositivi di rete, possono essere integrati a livello di package. Il secondo implementa la connettività fuori package utilizzando diversi tipi di connessione (ottica, cavo elettrico, mmWave) e retimer UCIe.

I retimer trasmettono il protocollo sottostante (PCIe, CXL) al livello di rack o pod e consentono la condivisione delle risorse.

Il consorzio rivendica un aumento notevole delle prestazioni come da tabella seguente.

Il nuovo consorzio segue altri standard lanciati da Intel, come CXL, bus PCI, PCI Express e USB. Das Sharma prevede una lungo periodo di innovazione che il consorzio può portare e afferama: “Questo è davvero il modo in cui verranno costruiti i SoC”.

Le società fondatrici sono in procinto di finalizzare l’accordo come organismo di standard aperto e prevedono di farlo entro la fine dell’anno. Le aziende associate inizieranno quindi a lavorare sulla prossima generazione di tecnologia UCIe, dal design alla sicurezza.

Cosa dicono le aziende partecipanti.

A conclusione di questa panoramica sono molto interessanti alcune dichiarazioni delle aziende consorziate.

“AMD è orgogliosa di continuare la nostra lunga storia di supporto agli standard del settore che possono consentire soluzioni innovative che soddisfano le esigenze in evoluzione dei nostri clienti. Siamo stati leader nella tecnologia chiplet e diamo il benvenuto a un ecosistema di chiplet multi-vendor per consentire l’integrazione personalizzabile di terze parti. Lo standard UCIe sarà un fattore chiave per guidare l’innovazione dei sistemi sfruttando motori di elaborazione e acceleratori eterogenei che consentiranno le migliori soluzioni ottimizzate per prestazioni, costi ed efficienza energetica”, ha affermato Mark Papermaster, vicepresidente esecutivo e chief technology officer di AMD.

“L’integrazione di più chiplet in un package per fornire innovazione di prodotto in tutti i segmenti di mercato è il futuro dell’industria dei semiconduttori e un pilastro della strategia IDM 2.0 di Intel. Fondamentale per questo futuro è un ecosistema chiplet aperto con i principali partner del settore che lavorano insieme nell’ambito del consorzio UCIe verso l’obiettivo comune di trasformare il modo in cui l’industria offre nuovi prodotti e continua a mantenere la promessa della legge di Moore”, ha affermato Sandra Rivera, vice presidente e direttore generale, data center e intelligenza artificiale, di Intel.